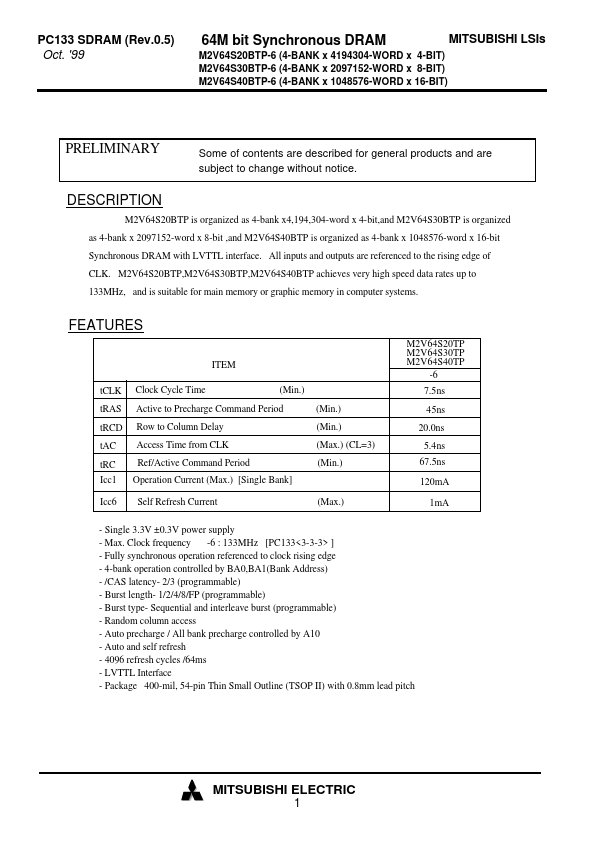

S40B

Description

M2V64S20BTP is organized as 4-bank x4,194,304-word x 4-bit,and M2V64S30BTP is organized as 4-bank x 2097152-word x 8-bit ,and M2V64S40BTP is organized as 4-bank x 1048576-word x 16-bit Synchronous DRAM with LVTTL interface.

Key Features

- Single 3.3V ±0.3V power supply

- Fully synchronous operation referenced to clock rising edge

- /CAS latency- 2/3 (programmable)

- Burst length- 1/2/4/8/FP (programmable)

- Burst type- Sequential and interleave burst (programmable)

- Random column access

- Auto precharge / All bank precharge controlled by A10 - Auto and self refresh

- 4096 refresh cycles /64ms

- LVTTL Interface